Programmable ASICs Will Change Infrastructure Investments

With any technology, whether it’s consumer technology or enterprise IT, it’s only a matter of time from the purchase before the technology is outdated. Most IT departments are extremely good by now with understanding the refresh cycle and how hardware depreciates over time. I learned of some technology at Cisco Live Europe this week that is going to revolutionize the way the buying cycle (at least with regard to switches) works. To understand why this is so important, we first need to understand the silicon that is used in a piece of IT hardware.

Processing Power

There are a few distinct ways that physical processing power can be developed and placed inside an infrastructure component like a switch.

- General purpose CPU (x86)

- Field-programmable Gate Array

- Application-specific Integrated Circuit

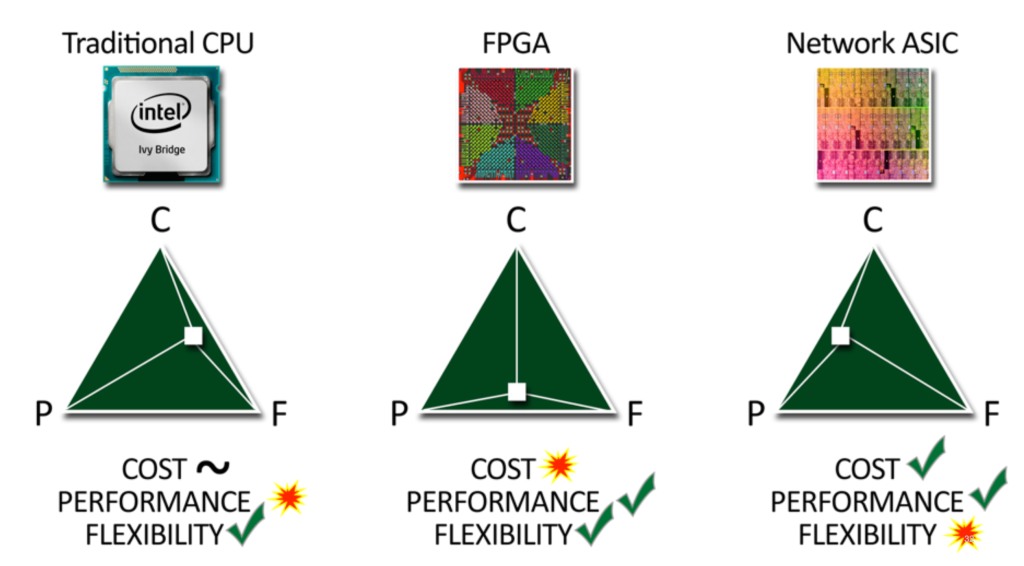

The design decision regarding which of these types of chips to use has to do with balancing tradeoffs. As you can see in Figure 1 which is from Dave‘s slide deck, the tradeoffs are as such:

- CPU: Sacrifice performance for application flexibility.

- FPGA: Sacrifice cost for performance and application flexibility.

- ASIC: Sacrifice flexibility for raw performance.

There are unique use cases for choosing one other the other, but consider an example of both ends of the spectrum. A desktop computer uses an x86 CPU that can run the operating system and all sorts of applications. On the other hand, an average Cisco switch is built with ASICs built specifically to switch frames or route packets (and other networking tasks). The switch’s ASICs perform a limited, specific set of functions extremely well. But they don’t do anything else. On the other hand, the CPU in the desktop computer can do just about anything, but it comes at the cost of performance.

The Depreciation Challenge

In the case of enterprise switching, the design decision is usually to use ASICs for the performance boost compared to the other two options. The biggest problem with this is that if a new ASIC-level feature is finished 3 months after the switch was purchased, it won’t be available to customers on the 3-month-old switch. A new batch of ASICs will need to be produced with the new feature integrated and only newly manufactured switches will include the feature.

Over the course of the IT hardware lifecycle, decisions to replace gear are based on things like support contracts and such. But they’re also based on the availability of features as compared to business requirements. The challenge with traditional ASICs in the lifecycle is that a business requirement might necessitate that a certain feature is implemented that is not available on switches that are only 6 months old. Unfortunately, this can force IT organizations to have no choice but to stomach the cost of a new hardware purchase.

This is not brand new technology (it’s been in the Catalyst 3850 for a bit of time now, I think) but Cisco has developed something I just heard about for the first time that will make a big difference in addressing business challenges like this.

Unified Access Data Plane ASIC

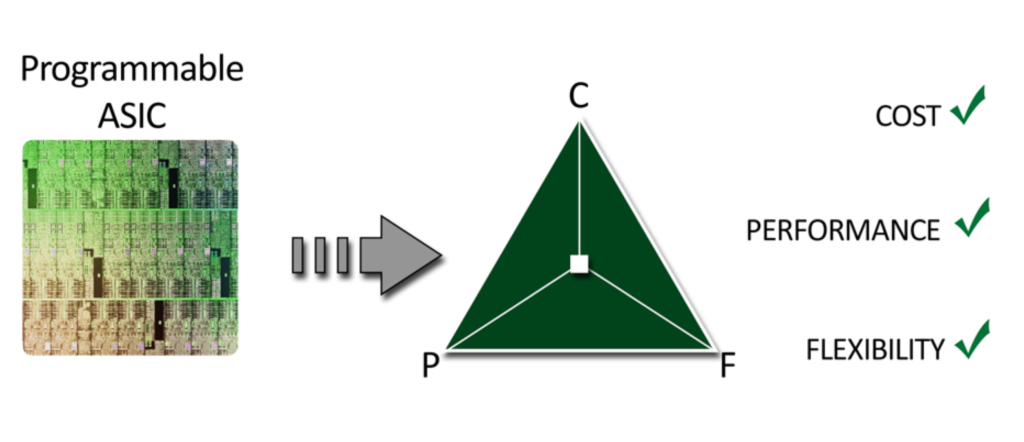

To make a long story short, the UADP chip (the name has to do with unifying wired+wireless, which is unrelated) shown in the header picture (autographed by Peter, one of the folks heavily involved in the project) is a programmable ASIC. This means that it comes with the application-specific performance that switch manufacturers have always chosen ASICs for, but it can be upgraded with new hardware-level code after it’s already in the field.

This means that if Cisco develops a new feature that will solve the business challenge an organization is facing and the 3850 is capable, a microcode update to the ASIC can enable the feature in a situation that would require the purchase of a new switch under any standard ASIC architecture. This is huge in that businesses will be able to delay the purchase of new equipment until necessary for another reason. There will, of course, still be reasons that switches need to be replaced. Other components will still become outdated. But the ability to introduce new hardware-level features on a unit is already deployed to the field is super exciting to me.

The UADP chip has many other interesting features as well, so it’s certainly even more exciting than just the programmability. But the microcode update ability of the chip which enables the balance of tradeoffs shown in Figure 2 is the most exciting feature to me.

To learn more about the big picture of the UADP technology, be sure to watch the Tech Field Day Extra video – the entire thing is riveting, and I don’t say that lightly. Thanks to Cisco Live EMEA and Tech Field Day for having me out for this presentation!